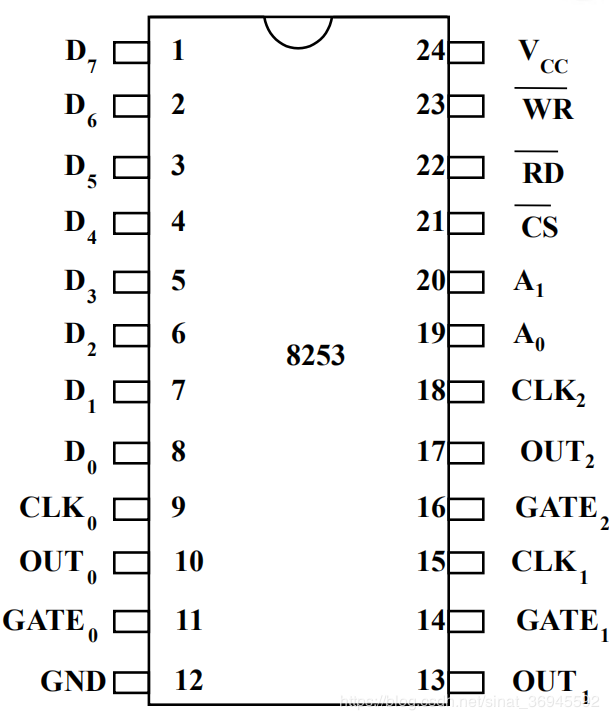

引脚

双列直插,24根引脚

引脚功能

数据端口

D7~D0:8位三态双向缓冲器

接收CPU送来的数据(计数值)和控制信息(控制字)。

高阻态:隔离芯片与系统总线。

连接系统数据总线

读/写控制逻辑

~CS:片选信号输入引脚,低电平有效

~RD:读信号输入引脚,低电平有效

~WR:写信号输入引脚,低电平有效

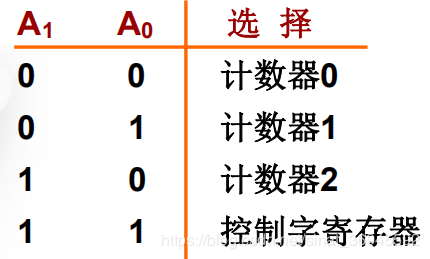

A1、A0:端口选择信号输入引脚

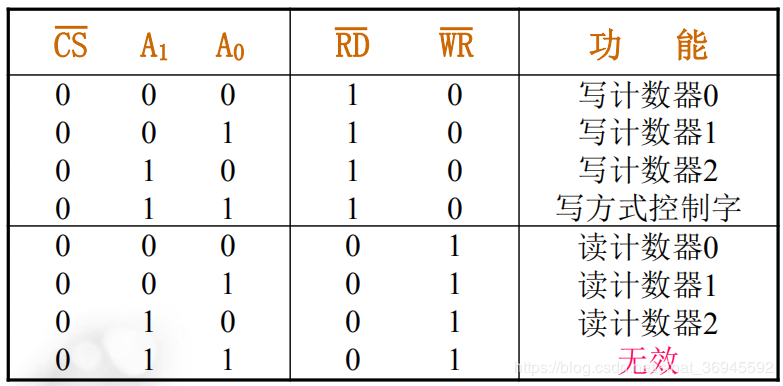

8253的端口操作

计数器通道0、1、2

三个通道完全相同

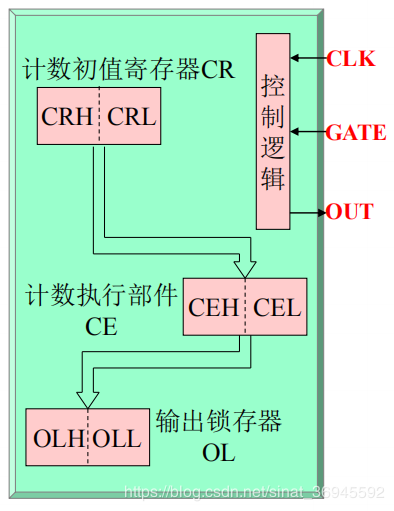

计数初值寄存器CR

16位,存放计数初值,在计数/定时启动之前设定

计数器执行部件CE

16位减1计数器,初值=CR值,CLK引脚每出现一个脉冲,计数值减1。减至零时,OUT引脚输出电平或脉冲信号,CPU不能直接访问。

输出锁存器OL

16位,锁存CE值,跟随CE变化,使用锁存命令来锁定当前计数值

相应引脚

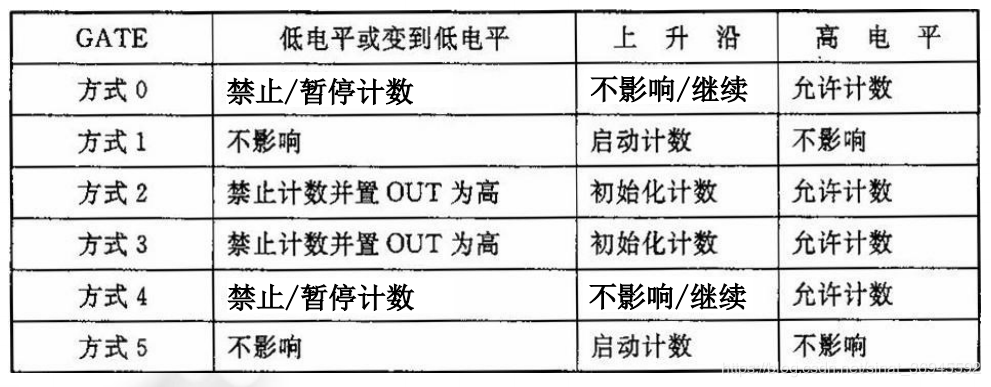

门控信号输入端GATEn:允许/禁止、启动/停止计数

脉冲信号输入端CLKn:时钟脉冲频率不能大于2MHz

计数/定时完成信号输出端OUTn:以电平或脉冲方式

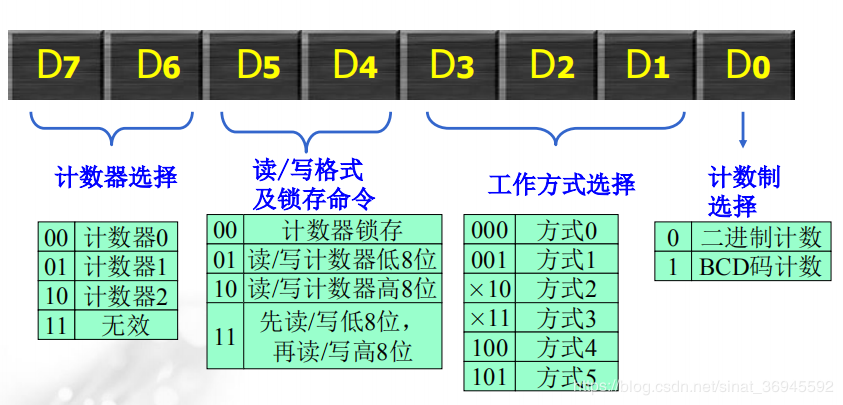

控制字寄存器

8位,存放CPU送来的控制字

用于选定计数器通道及其工作方式,指定计数初值的读写格式和表示方式

启动方式

软件

写入计数初值后的第1个CLK脉冲的下降沿开始计数,前提条件是GATE引脚保持高电平。

硬件

由门控信号GATE的上升沿触发开始计数。

工作方式

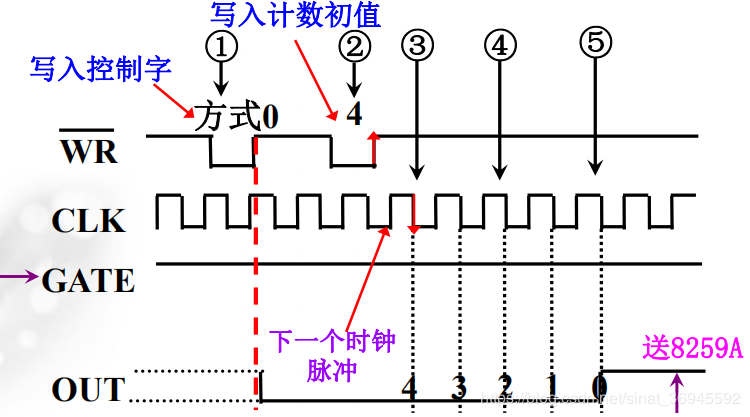

方式0(计数结束中断)(软件启动)

控制字写入后,OUT引脚输出低电平。

计数初值写入后的下一个CLK脉冲,开始计数。

计数值减为0时,OUT引脚输出高电平。

特点:计数初值不会自动重装,只计数一遍。(OUT保持高电平)

计数过程中,新的计数初值,触发重新开始计数。

GATE信号:“1”允许计数,“0”停止计数。从低变为高时,继续计数。

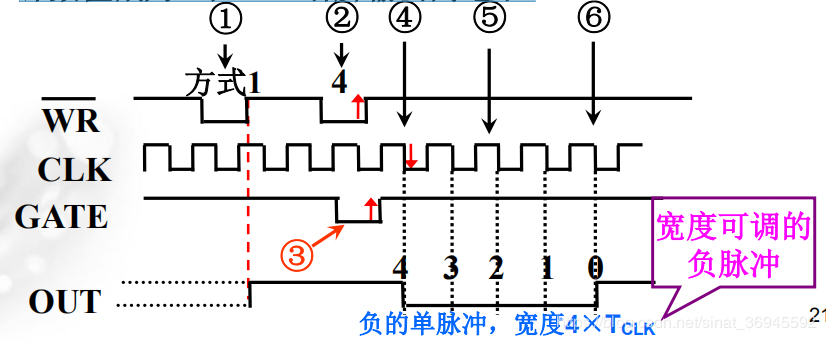

方式1(可编程单稳态输出)(硬件启动)

控制字写入后,OUT引脚输出高电平。

计数初值写入后,OUT引脚保持高电平。

GATE门控信号上升沿后的下一个CLK脉冲,开始计数。同时,OUT引脚变为低电平。

计数值减为0时,OUT引脚输出高电平。

特点:计数初值不会自动重装,GATE引脚上升沿可实现重装

计数过程中,GATE引脚上升沿,触发重新计数

计数过程中,写入新初值不影响本次计数。

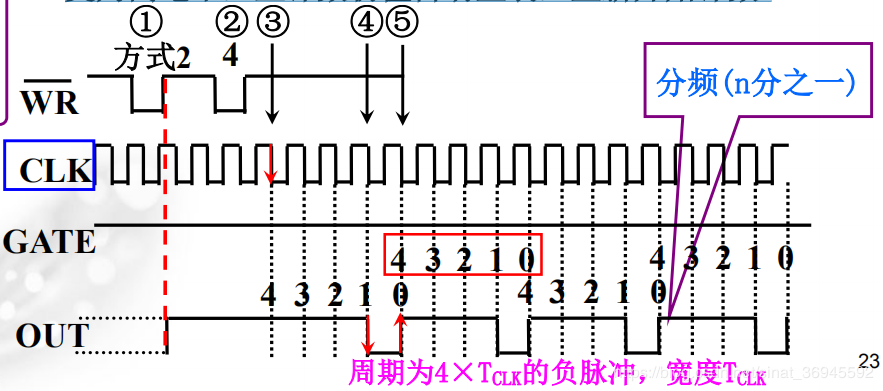

方式2(比率发生器)(软硬件启动)

控制字写入后,OUT引脚输出高电平

计数初值写入后的下一个CLK脉冲,开始计数

计数值减到1时,OUT引脚输出低电平,维持一个Tclk,又

变为高电平,且计数初值自动重装,重新开始计数。

特点:自动重装计数初值

计数过程中,GATE引脚变低,暂停计数;GATE引脚出现上升沿,重新开始计数。——硬件启动

计数过程中写入新初值影响下次计数

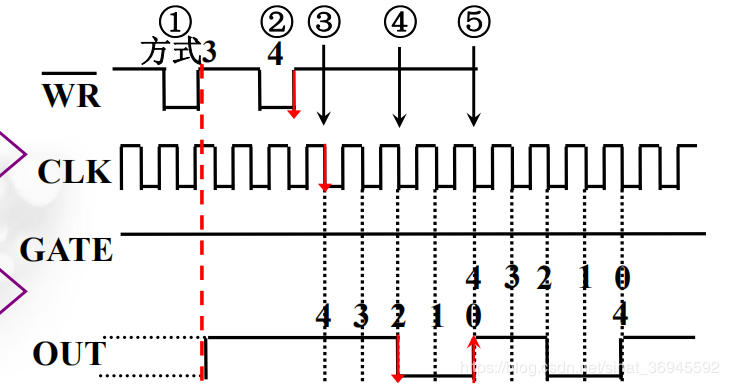

方式3(方波发生器)(软硬件启动)

//前N/2或(N+1)/2个CLK ,OUT为高//

//后N/2或(N-1)/2个CLK,OUT为低//

控制字写入后,OUT引脚输出高电平。

计数初值写入后的下一个CLK脉冲,开始计数

当计数到一半值时,OUT引脚输出变低,直至计数到0。OUT引脚输出高,计数初值自动重装,重新开始计数

特点:自动重装计数初值,输出方波信号

计数过程中,GATE引脚变低,暂停计数;GATE引脚出现上升沿,重新开始计数。——硬件启动

计数过程中写入新初值,影响下次计数

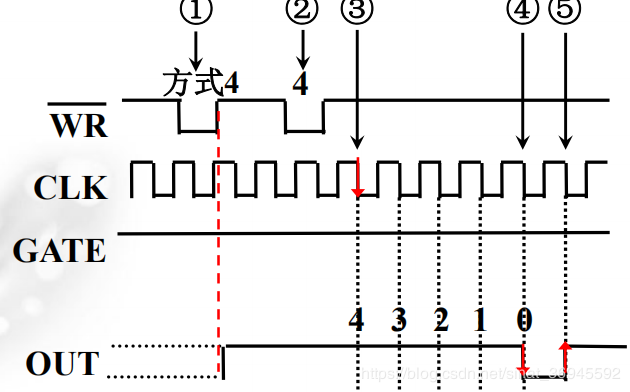

方式4(软件触发选通)(软件启动)

控制字写入后,OUT引脚输出高电平

计数初值写入后的下一个CLK脉冲,开始计数

计数值减到0时,OUT引脚输出低电平,维持一个TCLK,又变为高电平,计数停止

特点:计数初值不会自动重装

当GATE=1时,允许计数;GATE=0时,停止计数

计数过程中改变计数值,按新值重新开始计数

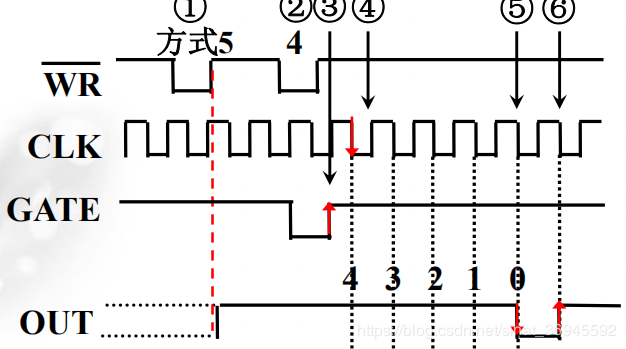

方式5(硬件触发选通)(硬件启动)

控制字写入后,OUT引脚输出高电平

计数初值写入后,待GATE引脚出现上升沿后,从下一个CLK脉冲开始计数

计数值减到0时,OUT引脚输出低电平,维持一个TCLK,又变为高电平,计数停止

特点:计数初值不会自动重装

计数过程中,若改变计数初值,仅当GATE上升沿才按新计数值重新开始计数

计数过程中出现GATE上升沿,重新开始计数

对比

初始化编程

先写控制字,再送计数初值

计数初值一次只能写入8位(先写低8位,后写高8位(可不写))

控制字写入控制口,每个计数器的计数初值写入各自计数器口

写入的顺序:按通道序号分别写入,按内容分别写入

8253方式控制字